For example if it detects that the same field is read in a loop, it could decide to hoist that variable out of the loop as is shown below.

#Mesi cache coherence simulator#

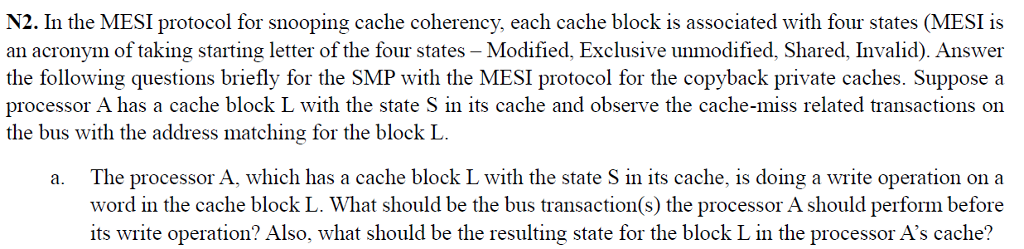

In this paper, an Android-based educational MESI cache coherence simulator is presented that shows with. There are 4 input commands a private cache may get for a cacheline. Each private cache is connected to its own processor core as well as a common busthat is shared among other private caches. 1.The cache line changes state for an event triggered by the processor or the interconnect (i.e. 1 Cache Coherence: MESI Assume you are designing a MESI snoopy bus cache coherence protocol for write-back private caches in amulti-core processor. The MESI protocol operates per cache line, and it can be any of the four states, which we have discussed in Fig. 1 shows a state diagram of a standard four states MESI protocol. For example, 1) they use a global serializing point to serialize transactions, 2) they designed a lot messaging types such as INV, RESP and so on. The techniques and protocols from this paper are similar to the exisiting ones. This information appears on special signal. The MESI (Modified-Exclusive- Shared-Invalid) cache coherence protocol is one of them. The most common cache coherence protocol is the MESI protocol. In this work, the add MESI coherence to these private L1 caches, as in they can make multiple L1 cache cache-coherent. Transition between the states is controlled by memory accesses and bus snooping activity. Its acronym stands for modified, exclusive, shared, invalid and refers to the states that cached data can take. The issue here is that the compiler (JIT in this case) has a lot of freedom to optimize code. The MESI protocol is a formal mechanism for controlling cache coherency using snooping techniques. This is the domain of the MESI protocol.Īssuming that every put and get in the Java bytecode is translated (and not optimized away) to a store and a load on the CPU, then even without volatile, every get would see the most recent put to the same address. So it won't happen that after one CPU commits the store to some variable to the cache, another CPU will still load the old value for that variable. The MESI (Modified-Exclusive-Shared-Invalid) cache coherence protocol is one of them.

Volatile prevents 3 different flavors of problems:įirst of all, caches on the X86 are always coherent.

0 kommentar(er)

0 kommentar(er)